# SC8F37xx User Manual

Enhanced 8-bit CMOS Microcontroller with Flash Memory Rev. 1.4.0

Please be reminded about following CMS's policies on intellectual property

- \* The name of Cmsemicron Limited and logo are both trademarks of our company.

- \*Our company preserve the rights to further elaborate on the improvements about products' function, reliability and design in this manual. However, our company is not responsible for any usage about this munal. The applications and their purposes in this manual are just for clarification, our company does not guarantee that these applications are feasible without further improvements and changes, and our company does not recommend any usage of the products in areas where people's safety is endangered during accident. Our company's products are not authorzed to be used for life-saving or life support devices and systems.our company has the right to change or improve the product without any notification, for latest news, please visit our website: www.mcu.com.cn

<sup>\*</sup> Cmsemicron Limited(denoted as 'our company' for later use) has already applied for relative patents and entitled legal rights. Any patents related to CMS's MCU or other producrts is not authorized to use. Any individual, organization or company which infringes s our company's interlectual property rights will be forbidden and stopped by our company through any legal actions, and our company will claim the lost and required for compensation of any damage to the company.

# **Contents**

| 1. PF | RODUCT DESCRIPTION                           |                |

|-------|----------------------------------------------|----------------|

| 1.1   | Features                                     |                |

| 1.2   | SYSTEM BLOCK DIAGRAM                         | 2              |

| 1.3   | PINOUT                                       |                |

| 1.3   | 3.1 SC8F3751                                 |                |

| 1.3   | 3.1 SC8F3752                                 |                |

| 1.3   | 3.2 SC8F3792                                 |                |

| 1.4   | SYSTEM CONFIGURATION REGISTER                | 6              |

| 1.5   | Online serial programming                    | 7              |

| 2. CE | ENTRAL PROCESSING UNIT (CPU)                 | 8              |

| 2.1   | Memory                                       |                |

| 2.1   | I.1 Program memory                           |                |

| 2.1   | 1.2 Data memory                              | 1 <sup>2</sup> |

| 2.2   | Addressing modes                             | 16             |

| 2.2   | 2.1 Direct addressing                        | 16             |

| 2.2   | 2.2 Immediate addressing                     | 16             |

| 2.2   | 2.3 Indirect addressing                      |                |

| 2.3   | Stack                                        |                |

| 2.4   | ACCUMULATOR (ACC)                            | 18             |

| 2.4   | 1.1 Overview                                 | 18             |

| 2.4   | 1.2 ACC applications                         | 18             |

| 2.5   | Program status register (STATUS)             | 19             |

| 2.6   | Pre-scaler (OPTION_REG)                      | 2 <sup>2</sup> |

| 2.7   | PROGRAM COUNTER (PC)                         | 23             |

| 2.8   | WATCHDOG TIMER (WDT)                         | 25             |

| 2.8   | 3.1 WDT period                               | 25             |

| 2.8   | 3.2 Watchdog timer control register (WDTCON) | 26             |

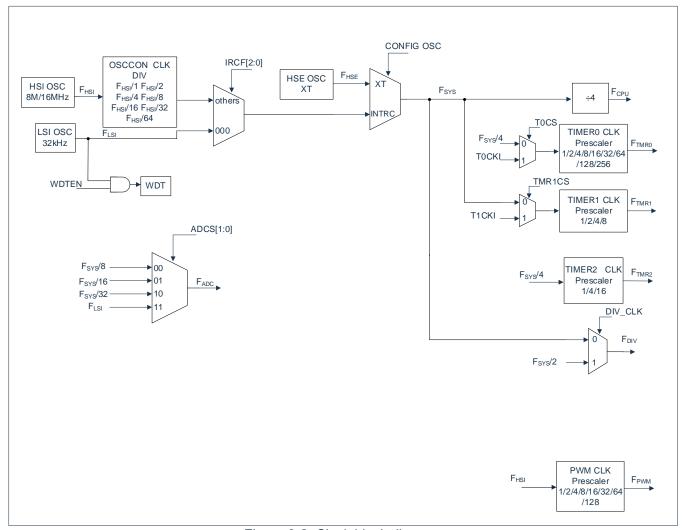

| 3. SY | YSTEM CLOCK                                  | 27             |

| 3.1   | Overview                                     | 27             |

| 3.2   | SYSTEM OSCILLATOR                            | 29             |

| 3.2   | 2.1 Internal RC oscillation                  | 29             |

| 3.2   | 2.2 External XT oscillation                  | 29             |

| 3.3   | Reset time                                   | 29             |

| 3.4   | OSCILLATOR CONTROL REGISTER                  | 30             |

| 3.5   | CLOCK BLOCK DIAGRAM                          | 3              |

| 4. RE | ESET                                         |                |

| 4.1   | Power-on reset                               |                |

| 4.2   | Power-off reset                              |                |

| 4.2   |                                              |                |

| 4.2   |                                              |                |

| 4.3   | WATCHDOG RESET                               |                |

| •     |                                              |                |

| 5. \$ | SLE   | EP MODE                                        | 36             |

|-------|-------|------------------------------------------------|----------------|

| 5.1   | E     | ENTER SLEEP MODE                               | 36             |

| 5.2   | 1     | AWAKEN FROM SLEEP MODE                         | 36             |

| 5.3   | I     | INTERRUPT AWAKENING                            | 37             |

| 5.4   | 5     | SLEEP MODE APPLICATION EXAMPLES                | 37             |

| 5.5   |       | SLEEP MODE WAKE-UP TIME                        | 38             |

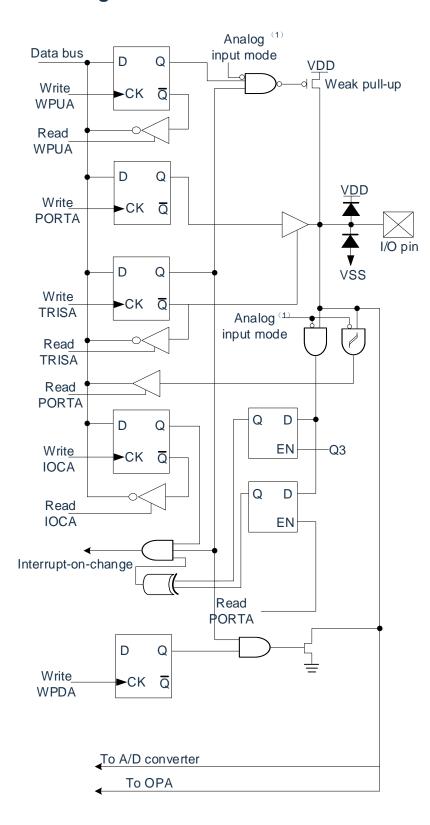

| 6. I  | /O F  | PORTS                                          | 39             |

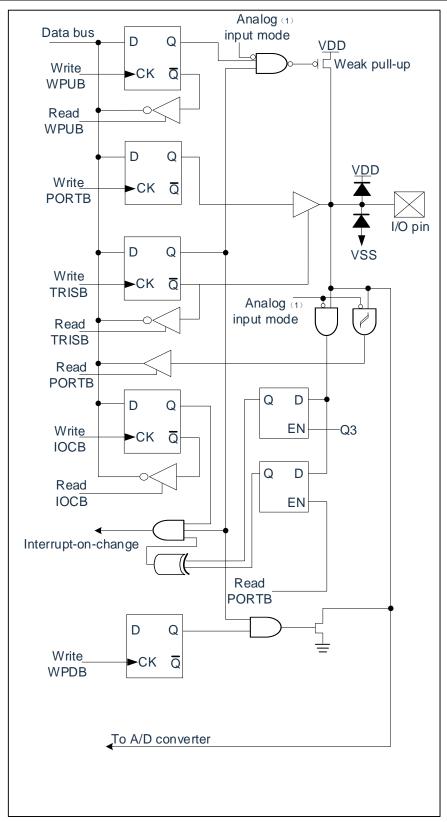

| 6.1   | I     | I/O PORT BLOCK DIAGRAM                         | 40             |

| 6.2   | F     | PORTA                                          | 42             |

| 6     | 3.2.1 | PORTA data and direction control               | 42             |

| 6     | 5.2.2 | PORTA analog selection control                 | 43             |

| 6     | 5.2.3 | PORTA pull-up resistance                       | 43             |

| 6     | 3.2.4 | PORTA pull-down resistance                     | 44             |

| 6     | 3.2.5 | PORTA interrupt on change                      | 44             |

| 6.3   | F     | PORTB                                          | 46             |

| 6     | 3.3.1 | PORTB data and direction                       | 46             |

| 6     | 3.3.2 | PORTB analog selection control                 | 47             |

| 6     | 3.3.3 | PORTB pull-down resistance                     | 47             |

| 6     | 5.3.4 | PORTB pull-up resistance                       | 48             |

| 6     | 3.3.5 | PORTB interrupt on change                      | 48             |

| 6.4   | I     | I/O usage                                      | 50             |

| 6     | 3.4.1 | Write I/O port                                 | 50             |

| 6     | 6.4.2 | Read I/O port                                  | 50             |

| 6.5   | (     | Cautions for I/O port usage                    | 5 <sup>1</sup> |

| 7. I  | NTE   | ERRUPT                                         | 52             |

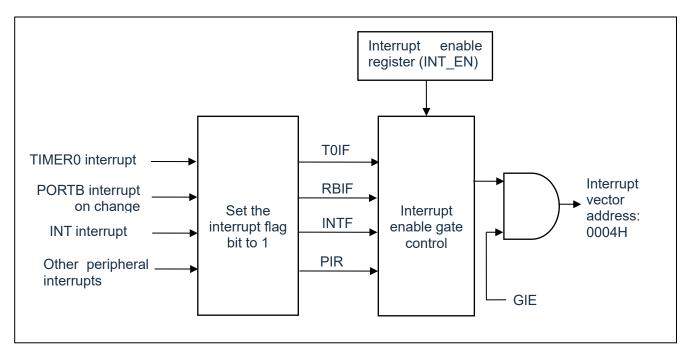

| 7.1   | (     | Overview                                       | 52             |

| 7.2   | I     | NTERRUPT CONTROL REGISTER                      | 53             |

| 7     | 7.2.1 | Interrupt control register                     | 53             |

| 7     | 7.2.2 | Peripheral interrupt enable register           | 54             |

| 7     | 7.2.3 | Peripheral interrupt request register          | 55             |

| 7.3   | F     | PROTECTION METHODS FOR INTERRUPT               | 56             |

| 7.4   | I     | NTERRUPT PRIORITY AND MULTI-INTERRUPT NESTING  | 56             |

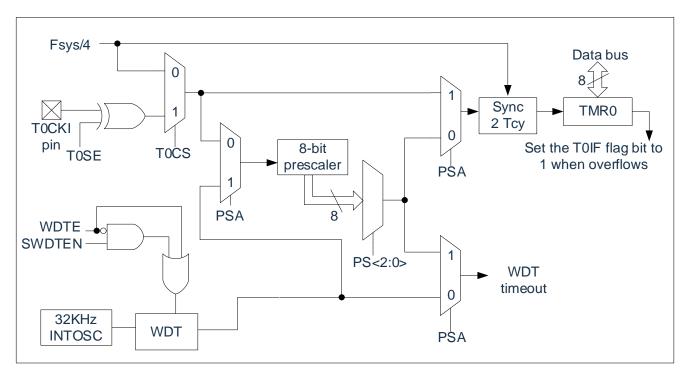

| 8. 7  | TIME  | ER0                                            | 57             |

| 8.1   | (     | Overview                                       | 57             |

| 8.2   | ١     | Working principle for TIMER0                   | 58             |

| 8     | 3.2.1 | 8-bit timer mode                               | 58             |

| 8     | 3.2.2 | 8-bit counter mode                             | 58             |

| 8     | 3.2.3 | Software programmable pre-scaler               | 58             |

| 8     | 3.2.4 | Switch prescaler between TIMER0 and WDT module |                |

| 8     | 3.2.5 | TIMER0 interrupt                               |                |

| 8.3   | -     | TIMERO RELATED REGISTERS                       | 6´             |

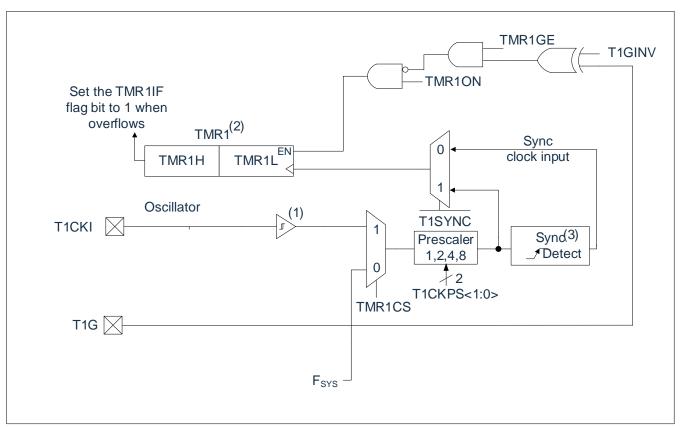

| 9. 7  | ТІМІ  | ER1                                            | 62             |

|       |       |                                                |                |

| 9   | .1 (         | Overview                                                         | 62 |

|-----|--------------|------------------------------------------------------------------|----|

| 9   | .2 ١         | Working principle for TIMER1                                     | 63 |

| 9   | .3 (         | CLOCK SOURCE SELECTION                                           | 63 |

|     | 9.3.1        | Internal clock source                                            | 63 |

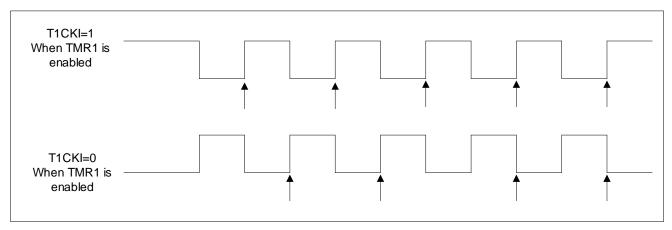

|     | 9.3.2        | External clock source                                            | 64 |

| 9   | .4           | FIMER1 pre-scaler                                                | 65 |

| 9   | .5           | FIMER1 WORKING PRINCIPLE IN ASYNCHRONOUS COUNTER MODE            | 65 |

|     | 9.5.1        | Read and write operations to TIMER1 in asynchronous counter mode | 65 |

| 9   | .6           | FIMER1 GATE CONTROL                                              | 66 |

| 9   | .7           | FIMER1 INTERRUPT                                                 | 66 |

| 9   | .8           | TIMER1 WORKING PRINCIPLE DURING SLEEP                            | 66 |

| 9   | .9           | FIMER1 CONTROL REGISTER                                          | 67 |

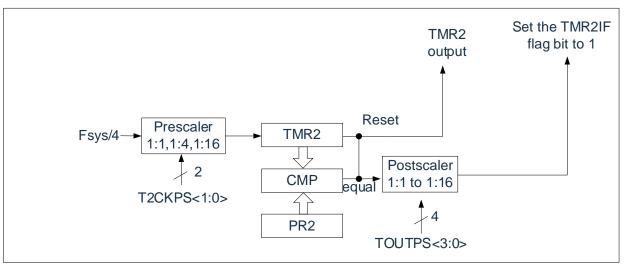

| 10. | TIME         | ER2                                                              | 68 |

| 1   | 0.1          | Overview                                                         | 68 |

| 1   | 0.2 \        | Working principle for TIMER2                                     | 69 |

| 1   | 0.3          | FIMER2 RELATED REGISTERS                                         | 70 |

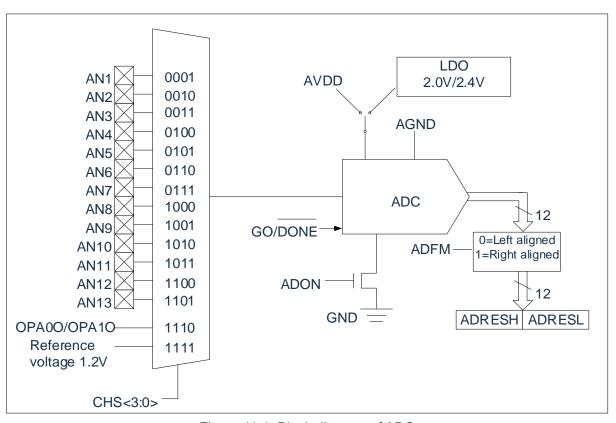

| 11. | ANA          | LOG TO DIGITAL CONVERSION (ADC)                                  | 71 |

|     |              | )<br>Dverview                                                    |    |

| 1   | 1.2 A        | ADC configuration                                                | 72 |

|     | 11.2.1       | Port configuration                                               | 72 |

|     | 11.2.2       | Channel selection                                                | 72 |

|     | 11.2.3       | ADC internal reference voltage                                   | 72 |

|     | 11.2.4       | ADC reference voltage                                            | 72 |

|     | 11.2.5       | Converter clock                                                  | 73 |

|     | 11.2.6       | ADC Interrupt                                                    | 73 |

|     | 11.2.7       | Result formatting                                                | 73 |

| 1   | 1.3 A        | ADC OPERATION PRINCIPLE                                          | 74 |

|     | 11.3.1       | Start conversion                                                 | 74 |

|     | 11.3.2       | Complete conversion                                              | 74 |

|     | 11.3.3       | Stop conversion                                                  | 74 |

|     | 11.3.4       | Working principle for ADC in sleep mode                          | 74 |

|     | 11.3.5       | AD conversion procedure                                          | 75 |

| 1   | 1.4 <i>A</i> | ADC RELATED REGISTERS                                            | 76 |

| 12. | PWN          | И MODULE                                                         | 79 |

| 1   | 2.1 F        | PIN CONFIGURATION                                                | 79 |

| 1   | 2.2 F        | RELATED REGISTER DESCRIPTION                                     | 79 |

| 1   | 2.3 F        | PWM PERIOD                                                       | 83 |

| 1   | 2.4 F        | PWM DUTY CYCLE                                                   | 83 |

| 1   | 2.5          | SYSTEM CLOCK FREQUENCY CHANGES                                   | 83 |

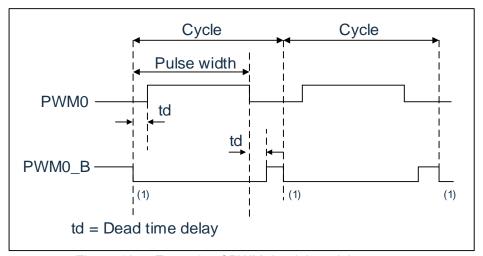

| 1   | 2.6 F        | PROGRAMMABLE DEAD-TIME DELAY MODE                                | 84 |

| 1   | 2.7 F        | PWM CONFIGURATION                                                | 84 |

| 13. | PRO          | GRAM EEPROM AND PROGRAM MEMORY CONTROL                           | 85 |

|     |              |                                                                  |    |

| 13.1   | Overview                                           | 85  |

|--------|----------------------------------------------------|-----|

| 13.2   | RELATED REGISTERS                                  | 86  |

| 13.    | 2.1 EEADR and EEADRH registers                     | 86  |

| 13.    | 2.2 EECON1 and EECON2 Registers                    | 86  |

| 13.3   | READ PROGRAM EEPROM                                | 88  |

| 13.4   | WRITE PROGRAM EEPROM                               | 89  |

| 13.5   | READ PROGRAM MEMORY                                | 90  |

| 13.6   | WRITE PROGRAM MEMORY                               | 90  |

| 13.7   | Cautions on Program EEPROM                         |     |

| 13.    | 7.1 Program EEPROM burn-in time                    | 91  |

|        | 7.2 Write verification                             |     |

| 13.    | 7.3 Protection against miswrites                   | 91  |

| 14. OF | PERATIONAL AMPLIFIER (OPA0, OPA1)                  | 92  |

| 14.1   | OPA0                                               | 92  |

| 14.    | 1.1 OPA0 enable                                    | 92  |

| 14.    | 1.2 OPA0 port selection                            | 92  |

| 14.    | 1.3 OPA0 operation mode                            | 93  |

| 14.    | 1.4 OPA0 related registers                         | 94  |

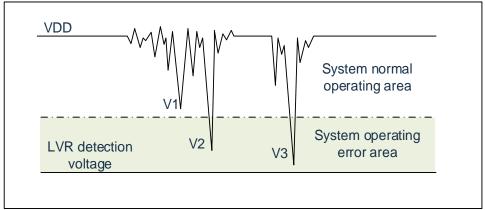

| 15. LC | OW VOLTAGE DETECTION (LVD)                         | 96  |

| 15.1   | Overview                                           | 96  |

| 15.2   | LVD RELATED REGISTERS                              | 96  |

| 15.3   | Operation of LVD                                   | 96  |

| 16. EL | ECTRICAL PARAMETERS                                | 97  |

| 16.1   | LIMIT PARAMETERS                                   | 97  |

| 16.2   | DC ELECTRICAL CHARACTERISTICS                      | 97  |

| 16.3   | ADC INTERNAL LDO REFERENCE VOLTAGE CHARACTERISTICS | 98  |

| 16.4   | OPA ELECTRICAL CHARACTERISTICS                     | 99  |

| 16.5   | LVR ELECTRICAL CHARACTERISTICS                     | 99  |

| 16.6   | AC ELECTRICAL CHARACTERISTICS                      | 100 |

| 17. IN | STRUCTIONS                                         | 101 |

| 17.1   | INSTRUCTION SET                                    | 101 |

| 17.2   | Description of instructions                        | 103 |

| 18. PA | ACKAGES                                            | 119 |

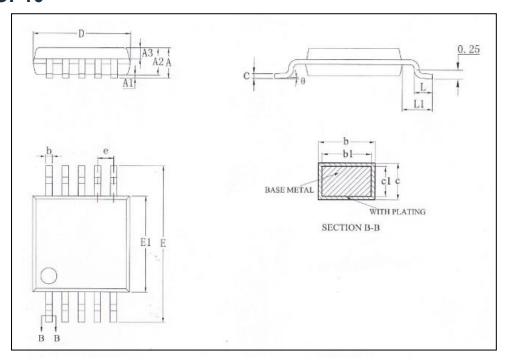

| 18.1   | MSOP10                                             |     |

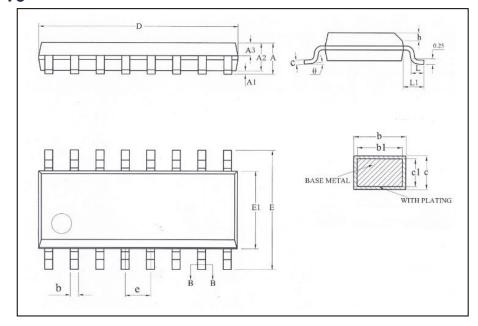

| 18.2   | SOP16                                              |     |

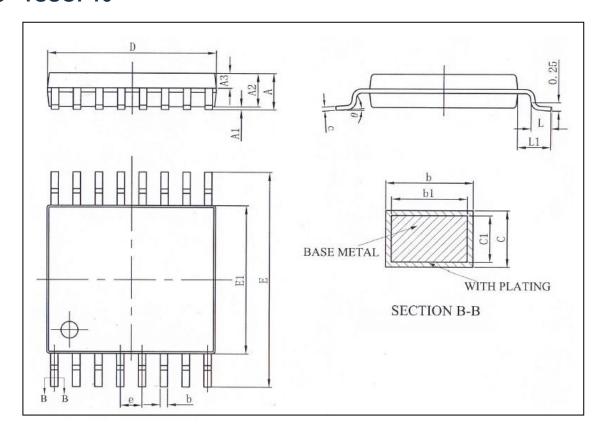

| 18.3   | TSSOP16                                            |     |

| 19. RF | EVISION HISTORY                                    |     |

# 1. Product Description

#### 1.1 Features

- Memory

- ROM: 4K×16Bit

- Universal RAM: 344×8Bit

- ◆ 8-level stack buffer

- Short and clear instruction system (68 commands)

- Instructions period (single instruction or double instructions)

- Jump table function

- Built-in low voltage detection circuit

- Built-in WDT timer

- ♦ Interrupt source

- 3 timer interrupts

- RA port interrupt on change

- RB port interrupt on change

- Other peripheral interrupts

- Timer

- 8-bit timer: TIMER0, TIMER2

- 16-bit timer: TIMER1

- ◆ Built-in LVD module

- Choice of voltage:

- 2.2V/2.4V/2.7V/3.0V/3.3V /3.7V/4.0V/4.3V

- Built-in 128-byte program EEPROM

- Rewritable times: 10,000

Operating voltage range: 3.5V—5.5V@16MHz1.8V—5.5V@8MHz

Operating temperature range: -20°C-75°C

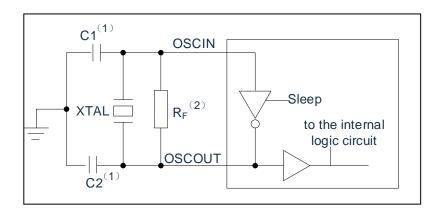

- Two oscillation methods

- Internal RC oscillation: design frequency 8MHz/16MHz

- External high-speed crystal oscillation: design frequency 8MHz

- ◆ PWM mod with complementary outputs

- 5-channel PWM, can be set to 2-channel complementary output

- 4-channel PWM with shared period and separated duty cycle

- 1-channel PWM with separated period and separated duty cycle

- Operational amplifier: 2-channel

- Offset voltage <2mv

- Can be used as a comparator

- High precision 12-bit ADC

- High precision 12-bit ADC

±1.5% @VDD=2.5V~5.5V T<sub>A</sub>=25°C

±2% @VDD=2.5V~5.5V T<sub>A</sub>=-20°C~75°C

Selectable internal reference source: 2V/2.4V

#### Product specification

| PRODUCT  | ROM   | RAM   | Pro EE | I/O | PWM | OPA | ADC        | PACKAGE |

|----------|-------|-------|--------|-----|-----|-----|------------|---------|

| SC8F3751 | 4Kx16 | 344x8 | 128x8  | 8   | 5   | 0   | 12Bit x 8  | MSOP10  |

| SC8F3752 | 4Kx16 | 344x8 | 128x8  | 14  | 5   | 2   | 12Bit x 13 | SOP16   |

| SC8F3792 | 4Kx16 | 344x8 | 128x8  | 14  | 5   | 2   | 12Bit x 13 | TSSOP16 |

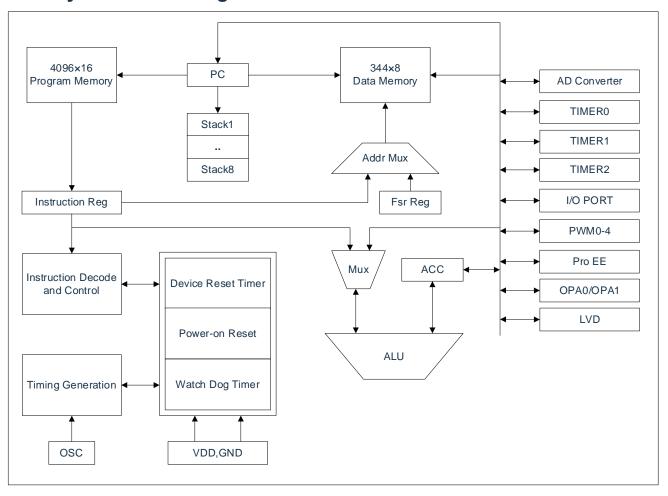

# 1.2 System block diagram

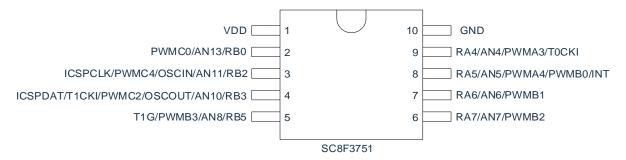

# 1.3 Pinout

#### 1.3.1 SC8F3751

#### SC8F3751 pin description:

| Pin name                         | IO type | Description                                                                                                    |

|----------------------------------|---------|----------------------------------------------------------------------------------------------------------------|

| VDD, GND                         | Р       | Supply voltage input pin, gound pin                                                                            |

| OSCIN/OSCOUT                     | I/O     | Crystal oscillator input/output pin                                                                            |

| RA4-RA7                          | I/O     | Programmable in/push-pull out pin, with pull-up resistance, pull-down resistance, interrupt on change function |

| RB0,RB2-RB3,RB5                  | I/O     | Programmable in/push-pull out pin, with pull-up resistance, pull-down resistance, interrupt on change function |

| ICSPCLK                          | 1       | Programmable input clock pin                                                                                   |

| ICSPDAT                          | I/O     | Programmable data input/output pin                                                                             |

| AN4-AN7, AN8,<br>AN10-AN11, AN13 | 1       | 12-bit ADC input pin                                                                                           |

| PWMx                             | 0       | PWM output function                                                                                            |

| INT                              | 1       | External interrupt input pin                                                                                   |

| T0CKI                            | I       | TIMER0 external clock input pin                                                                                |

| T1CKI                            | I       | TIMER1 external clock input pin                                                                                |

| T1G                              | 1       | TIMER1 external gate control input pin                                                                         |

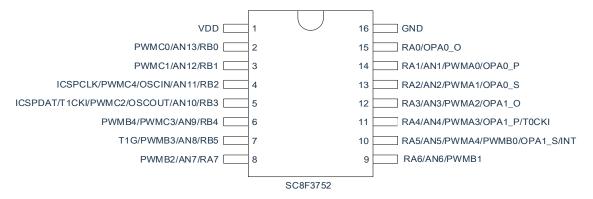

#### 1.3.1 SC8F3752

#### SC8F3752 pin description:

| Pin name     | IO type | Description                                                                                                    |  |  |  |

|--------------|---------|----------------------------------------------------------------------------------------------------------------|--|--|--|

| VDD,GND      | Р       | Supply voltage input pin, gound pin                                                                            |  |  |  |

| OSCIN/OSCOUT | I/O     | Crystal oscillator input/output pin                                                                            |  |  |  |

| RA0-RA7      | I/O     | Programmable in/push-pull out pin, with pull-up resistance, pull-down resistance, interrupt on change function |  |  |  |

| RB0-RB5      | I/O     | Programmable in/push-pull out pin, with pull-up resistance, pull-down resistance, interrupt on change function |  |  |  |

| ICSPCLK      | 1       | Programmable input clock pin                                                                                   |  |  |  |

| ICSPDAT      | I/O     | Programmable data input/output pin                                                                             |  |  |  |

| AN1-AN13     | 1       | 12-bit ADC input pin                                                                                           |  |  |  |

| PWMx0-PWMx4  | 0       | PWM0-4 output function                                                                                         |  |  |  |

| OPAx_P       | I       | Op-amp positive input pin                                                                                      |  |  |  |

| OPAx_S       | 1       | Op-amp negative input pin                                                                                      |  |  |  |

| OPAx_O       | 0       | Op-amp output pin                                                                                              |  |  |  |

| INT          | I       | External interrupt input pin                                                                                   |  |  |  |

| T0CKI        | I       | TIMER0 external clock input pin                                                                                |  |  |  |

| T1CKI        | I       | TIMER1 external clock input pin                                                                                |  |  |  |

| T1G          | I       | TIMER1 external gate control input pin                                                                         |  |  |  |

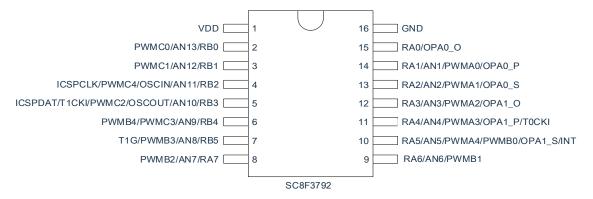

#### 1.3.2 SC8F3792

#### SC8F3792 pin description:

| Pin name     | IO type | Description                                                                                                    |

|--------------|---------|----------------------------------------------------------------------------------------------------------------|

| VDD,GND      | Р       | Supply voltage input pin, gound pin                                                                            |

| OSCIN/OSCOUT | I/O     | Crystal oscillator input/output pin                                                                            |

| RA0-RA7      | I/O     | Programmable in/push-pull out pin, with pull-up resistance, pull-down resistance, interrupt on change function |

| RB0-RB5      | I/O     | Programmable in/push-pull out pin, with pull-up resistance, pull-down resistance, interrupt on change function |

| ICSPCLK      | 1       | Programmable input clock pin                                                                                   |

| ICSPDAT      | I/O     | Programmable data input/output pin                                                                             |

| AN1-AN13     | 1       | 12-bit ADC input pin                                                                                           |

| PWMx0-PWMx4  | 0       | PWM0-4 output function                                                                                         |

| OPAx_P       | 1       | Op-amp positive input pin                                                                                      |

| OPAx_S       | 1       | Op-amp negative input pin                                                                                      |

| OPAx_O       | 0       | Op-amp output pin                                                                                              |

| INT          | 1       | External interrupt input pin                                                                                   |

| T0CKI        | I       | TIMER0 external clock input pin                                                                                |

| T1CKI        | I       | TIMER1 external clock input pin                                                                                |

| T1G          | I       | TIMER1 external gate control input pin                                                                         |

# 1.4 System configuration register

The system configuration register (CONFIG) is the ROM option for the initial conditions of the MCU. It can only be burned by the SC writer, and cannot be accessed and manipulated by the user. It contains the following contents:

- 1. OSC (choice of oscillation)

- ◆ INTRC Internal RC oscillation

- XT External crystal oscillation

- 2. INTRC SEL (internal oscillation frequency)

- ◆ INTRC8M F<sub>HSI</sub> choose internal 8MHz RC oscillation

- ♦ INTRC16M F<sub>HSI</sub> choose internal 16MHz RC oscillation

- 3. WDT (watchdog choice)

- ENABLE Enable watchdog timer

- DISABLE Disable watchdog timer

- 4. PROTECT (encyption)

- DISABLE Disable FLASH code encyption

- ◆ ENABLE Enable FLASH code encryption, after which the read value from burning the simulator is uncertain.

- 5. LVR SEL (low voltage detection selection)

- 1.8V When this reset voltage is selected, F<sub>HSI</sub> needs to select 8MHz

- ◆ 2.0V When this reset voltage is selected, F<sub>HSI</sub> needs to select 8MHz

- ♦ 2.6V When this reset voltage is selected, F<sub>HSI</sub> needs to select 8MHz

- ◆ 3.5V

- 6. PWM SEL (PWM output port selection)

- Group A PWM0-4=RA1, RA2, RA3, RA4, RA5

- ◆ Group B PWM0-4=RA5, RA6, RA7, RB5, RB4

- ◆ Group C PWM0-4=RB0, RB1, RB3, RB4, RB2

- 7. ICSPPORT SEL (simulation port function selection)

- ◆ ICSP

ICSPCLK and DAT ports remain as simulation ports, all functions are

- not available

- ♦ NORMAL ICSPCLK and DAT ports are normal function ports

# 1.5 Online serial programming

Can perform serial programming on MCU the final application circuit. Programming is done through the following:

- Power wire

- Ground wire

- Data wire

- Clock wire

This ensures users to use un-programmed devices to make circuit and only program the MCU just before the product being delivered. Therefore, the lastest version of firmware can be burned into the MCU.

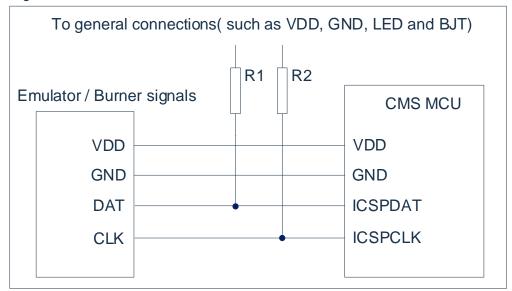

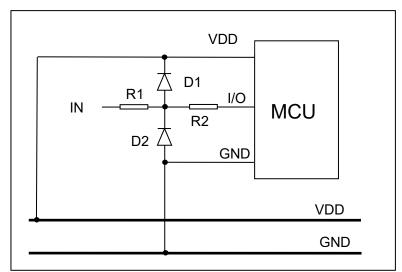

Figure 1-1: Typical connection for online serial programming

In the above figure, R1 and R2 are the electrical isolation devices, normally represented by resistor with the following resistance: R1 $\geq$ 4.7K, R2 $\geq$ 4.7K.

# 2. Central Processing Unit (CPU)

# 2.1 Memory

#### 2.1.1 Program memory

SC8F37xx program memory space

ROM: 4K

| 000H | Reset Vector              | Program start, jump to user program     |

|------|---------------------------|-----------------------------------------|

| 001H |                           |                                         |

| 002H |                           |                                         |

| 003H |                           |                                         |

| 004H | Interrupt vector          | Interrupt entry, user interrupt program |

|      |                           | User program area                       |

|      |                           |                                         |

|      |                           |                                         |

| FFDH |                           |                                         |

| FFEH |                           |                                         |

| FFFH | Jump to Reset Vector 000H | End of program                          |

#### 2.1.1.1 Reset vector (0000H)

MCU has 1-byte long system reset vector (000H). It has 3 ways to reset:

- ◆ Power-on reset

- Watchdog reset

- Low voltage reset (LVR)

When any above reset happens, program will start to execute from 0000H, system register will be recovered to default value. PD and TO from STATUS register can determine the which reset is performed from above. The following program illustrates how to define the reset vector from FLASH.

Example: define reset vector

|        | ORG | 0000H | ; system reset vector   |

|--------|-----|-------|-------------------------|

|        | JP  | START |                         |

|        | ORG | 0010H | ; start of user program |

| START: |     |       |                         |

|        | ••• |       | ; user program          |

|        |     |       |                         |

|        | END |       | ; program end           |

#### 2.1.1.2 Interrupt vector

The address for interrupt vector is 0004H. Once the interrupt responds, the current value for program counter (PC) will be saved to stack buffer and jump to 0004H to execute interrupt service program. All interrupts will enter 0004H. User will determine which interrupt to execute according to the bit of register of interrupt flag bit. The following program illustrates how to write interrupt service program.

Example: define interrupt vector, interrupt program is placed after user program

|            | ORG  | 0000H | ;system reset vector    |

|------------|------|-------|-------------------------|

|            | JP   | START |                         |

|            | ORG  | 0004H | ;start of user program  |

| INT_START: |      |       |                         |

|            | CALL | PUSH  | ;save ACC and STATUS    |

|            |      |       | ;user interrupt program |

|            |      |       |                         |

| INT_BACK:  |      |       |                         |

|            | CALL | POP   | ;back to ACC and STATUS |

|            | RETI |       | ;interrupt back         |

| START:     |      |       |                         |

|            |      |       | ;user program           |

|            |      |       |                         |

|            | END  |       | ;program end            |

Note: MCU does not provide specific unstack and push instructions, so user needs to protect interrupt scene.

### Example: interrupt-in protection

| <br>  |       |              |                           |  |

|-------|-------|--------------|---------------------------|--|

| PUSH: |       |              |                           |  |

|       | LD    | ACC_BAK,A    | ;save ACC to ACC_BAK      |  |

|       | SWAPA | STATUS       | ;swap half-byte of STATUS |  |

|       | LD    | STATUS_BAK,A | ;save to STATUS_BAK       |  |

|       | RET   |              | ;back                     |  |

#### Example: interrupt-out restore

| POP:  |            |                                                 |

|-------|------------|-------------------------------------------------|

| SWAPA | STATUS_BAK | ;swap the half-byte data from STATUS_BAK to ACC |

| LD    | STATUS,A   | ;pass the value in ACC to STATUS                |

| SWAPR | ACC_BAK    | ;swap the half-byte data in ACC_BAK             |

| SWAPA | ACC_BAK    | ;swap the half-byte data from ACC_BAK to ACC    |

| RET   |            | ;back                                           |

#### 2.1.1.3 **Jump table**

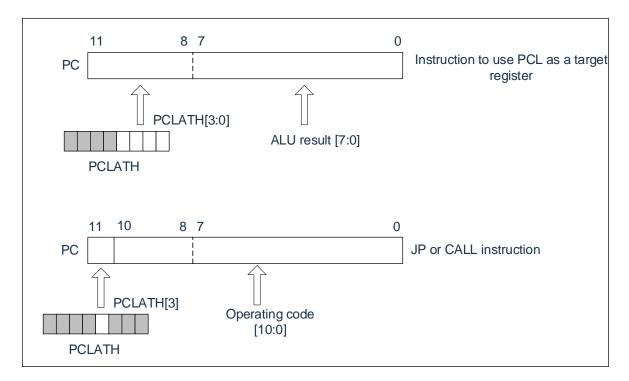

The jump table enables the multi-address jumping. Since the values of PCL and ACC can be added together to obtain a new PCL, multiple address jumps can be achieved by adding different ACC values to the PCL. If the ACC value is n, PCL+ACC means the current address plus n. The PCL value will also add 1 to itself after the current instruction is executed, see the following example. If an overflow occurs after PCL+ACC, the PC will not carry, so care should be taken when writing the program. In this way, the user can easily implement multi-address jumps by modifying the value of ACC.

PCLATH is the PC high-bit buffer register. When operating on PCL, you must first assign a value to PCLATH.

Example: Example of a correct multi-address jump program

|               |      | 1 11 3   |                                  |

|---------------|------|----------|----------------------------------|

| FLASH address |      |          |                                  |

|               | LDIA | 01H      |                                  |

|               | LD   | PCLATH,A | ;PCLATH must be assigned a value |

|               |      |          |                                  |

| 0110H:        | ADDR | PCL      | ;ACC+PCL                         |

| 0111H:        | JP   | LOOP1    | ;ACC=0, jump to LOOP1            |

| 0112H:        | JP   | LOOP2    | ;ACC=1, jump to LOOP2            |

| 0113H:        | JP   | LOOP3    | ;ACC=2, jump to LOOP3            |

| 0114H:        | JP   | LOOP4    | ;ACC=3, jump to LOOP4            |

| 0115H:        | JP   | LOOP5    | ;ACC=4, jump to LOOP5            |

| 0116H:        | JP   | LOOP6    | ;ACC=5, jump to LOOP6            |

Example: Example of an incorrect multi-address jump program

|               |      | , , , , | 3                             |

|---------------|------|---------|-------------------------------|

| FLASH address |      |         |                               |

|               | CLR  | PCLATH  |                               |

|               |      |         |                               |

| 00FCH:        | ADDR | PCL     | ;ACC+PCL                      |

| 00FDH:        | JP   | LOOP1   | ;ACC=0, jump to LOOP1         |

| 00FEH:        | JP   | LOOP2   | ;ACC=1, jump to LOOP2         |

| 00FFH:        | JP   | LOOP3   | ;ACC=2, jump to LOOP3         |

| 0100H:        | JP   | LOOP4   | ;ACC=3, jump to 0000H address |

| 0101H:        | JP   | LOOP5   | ;ACC=4, jump to 0001H address |

| 0102H:        | JP   | LOOP6   | ;ACC=5, jump to 0002H address |

Note: Since PCL overflow will not carry to the higher bits, the program cannot be placed at the partition of the FLASH space when using PCL to achieve multi-address jump.

# 2.1.2 Data memory

#### SC8F37xx data memory list

| or or ax data file           | Address |                      | ddress |                      | Address |                      | Address |

|------------------------------|---------|----------------------|--------|----------------------|---------|----------------------|---------|

| INDF                         | 00H     | INDF                 | 80H    | INDF                 | 100H    | INDF                 | 180H    |

| TMR0                         | 01H     | OPTION_REG           | 81H    | TMR0                 | 101H    | OPTION_REG           | 181H    |

| PCL                          | 02H     | PCL                  | 82H    | PCL                  | 102H    | PCL                  | 182H    |

| STATUS                       | 03H     | STATUS               | 83H    | STATUS               | 103H    | STATUS               | 183H    |

| FSR                          | 04H     | FSR                  | 84H    | FSR                  | 104H    | FSR                  | 184H    |

| PORTA                        | 05H     | TRISA                | 85H    | WDTCON               | 105H    |                      | 185H    |

| PORTB                        | 06H     | TRISB                | 86H    | PORTB                | 106H    | TRISB                | 186H    |

| WPDA                         | 07H     | IOCA                 | 87H    | PWMCON0              | 107H    |                      | 187H    |

| WPDB                         | 08H     |                      | 88H    | PWMCON1              | 108H    | ANSEL                | 188H    |

|                              | 09H     |                      | 89H    | PWMCON2              | 109H    | ANSELH               | 189H    |

| PCLATH                       | 0AH     | PCLATH               | 8AH    | PCLATH               | 10AH    | PCLATH               | 18AH    |

| INTCON                       | 0BH     | INTCON               | 8BH    | INTCON               | 10BH    | INTCON               | 18BH    |

| PIR1                         | 0CH     | PIE1                 | 8CH    | EEDAT                | 10CH    | EECON1               | 18CH    |

| PIR2                         | 0DH     | PIE2                 | 8DH    | EEADR                | 10DH    | EECON2               | 18DH    |

| TMR1L                        | 0EH     |                      | 8EH    | EEDATH               | 10EH    | WPUA                 | 18EH    |

| TMR1H                        | 0FH     | OSCCON               | 8FH    | EEADRH               | 10FH    | PWMTL                | 18FH    |

| T1CON                        | 10H     | OSCTUNE              | 90H    | TABLE_SPH            | 110H    | PWMTH                | 190H    |

| TMR2                         | 11H     |                      | 91H    | TABLE_SPL            | 111H    | PWMT4L               | 191H    |

| T2CON                        | 12H     | PR2                  | 92H    | TABLE_DATAH          | 112H    |                      | 192H    |

|                              | 13H     | PWM01DT              | 93H    |                      | 113H    | PWMD0L               | 193H    |

|                              | 14H     | PWM23DT              | 94H    |                      | 114H    | PWMD1L               | 194H    |

|                              | 15H     | WPUB                 | 95H    |                      | 115H    | PWMD2L               | 195H    |

|                              | 16H     | IOCB                 | 96H    |                      | 116H    | PWMD3L               | 196H    |

|                              | 17H     | LVDCON               | 97H    |                      | 117H    | PWMD4L               | 197H    |

|                              | 18H     |                      | 98H    |                      | 118H    |                      | 198H    |

|                              | 19H     |                      | 99H    |                      | 119H    |                      | 199H    |

|                              | 1AH     | OPA0CON              | 9AH    |                      | 11AH    |                      | 19AH    |

|                              | 1BH     | OPA0ADJ              | 9BH    |                      | 11BH    |                      | 19BH    |

|                              | 1CH     | OPA1CON              | 9CH    | PWMD01H              | 11CH    |                      | 19CH    |

|                              | 1DH     | OPA1ADJ              | 9DH    | PWMD23H              | 11DH    |                      | 19DH    |

| ADRESH                       | 1EH     | ADRESL               | 9EH    |                      | 11EH    |                      | 19EH    |

| ADCON0                       | 1FH     | ADCON1               | 9FH    |                      | 11FH    |                      | 19FH    |

|                              | 20H     |                      | A0H    |                      | 120H    |                      | 1A0H    |

|                              |         |                      |        |                      |         |                      |         |

|                              |         | General-purpose      |        | General-purpose      |         | General-purpose      |         |

| General-                     |         | register<br>80 bytes |        | register<br>80 bytes |         | register<br>80 bytes |         |

| purpose register<br>96 bytes |         | 00 Syloo             |        | 00 Syloo             |         | 00 <i>5</i> y 100    |         |

| 30 bytes                     | 6FH     |                      | EFH    |                      | 16FH    |                      | 1EFH    |

|                              | 70H     | Fact mamor:          | F0H    | Fact momon:          | 170H    | Fact moment          | 1F0H    |

|                              |         | Fast memory<br>space |        | Fast memory space    |         | Fast memory space    |         |

|                              | 7FH     | 70H-7FH              | FFH    | 70H-7FH              | 17FH    | 70H-7FH              | 1FFH    |

| BANK0                        |         | BANK1                |        | BANK2                |         | BANK3                |         |

Data memory consists of 512×8 bits. It can be divided into two space: special function register and general-purpose data memory. Most of data memory are able to write/read data, only some data memory is read-only. Special register address is from 00H-1FH, 80-9FH, 100-11FH, 180-19FH.

| Address | Name   | Bit7         | Bit6                                                       | Bit5                | Bit4           | Bit3         | Bit2           | Bit1              | Bit0        | Reset value |

|---------|--------|--------------|------------------------------------------------------------|---------------------|----------------|--------------|----------------|-------------------|-------------|-------------|

| 00H     | INDF   | Look-up for  | Look-up for this unit will use FSR, not physical register. |                     |                |              |                |                   |             | xxxxxxx     |

| 01H     | TMR0   | TIMER0 da    | nta register                                               |                     |                |              |                |                   |             | xxxxxxx     |

| 02H     | PCL    | Lower bit of | f program counte                                           | er                  |                |              |                |                   |             | 00000000    |

| 03H     | STATUS | IRP          | RP1                                                        | RP0                 | то             | PD           | Z              | DC                | С           | 00011xxx    |

| 04H     | FSR    | Indirect dat | a memory addre                                             | ess pointer         |                |              |                |                   |             | xxxxxxx     |

| 05H     | PORTA  | RA7          | RA6                                                        | RA5                 | RA4            | RA3          | RA2            | RA1               | RA0         | XXXXXXX     |

| 06H     | PORTB  |              |                                                            | RB5                 | RB4            | RB3          | RB2            | RB1               | RB0         | XXXXXX      |

| 07H     | WPDA   | WPDA7        | WPDA6                                                      | WPDA5               | WPDA4          | WPDA3        | WPDA2          | WPDA1             | WPDA0       | 00000000    |

| 08H     | WPDB   |              |                                                            | WPDB5               | WPDB4          | WPDB3        | WPDB2          | WPDB1             | WPDB0       | 000000      |

| 0AH     | PCLATH |              |                                                            |                     |                | Write buffer | for the high 4 | oits of the progr | ram counter | 0000        |

| 0BH     | INTCON | GIE          | PEIE                                                       | TOIE                | INTE           | RBIE         | TOIF           | INTF              | RBIF        | 00000000    |

| 0CH     | PIR1   | RAIF         | ADIF                                                       |                     |                | EEIF         | PWMIF          | TMR2IF            | TMR1IF      | 00000000    |

| 0DH     | PIR2   |              |                                                            |                     |                |              |                |                   | LVDIF       | 0           |

| 0EH     | TMR1L  | Data registe | er for the low by                                          | te of the 16-bit TI | MER1 register  |              |                |                   | _           | xxxxxxx     |

| 0FH     | TMR1H  | Data registe | er for the high by                                         | te of the 16-bit T  | IMER1 register |              |                |                   |             | xxxxxxx     |

| 10H     | T1CON  | T1GINV       | TMR1GE                                                     | T1CKPS1             | T1CKPS0        |              | T1SYNC         | TMR1CS            | TMR10N      | 0000-000    |

| 11H     | TMR2   | TIMER2 mo    | TIMER2 module register                                     |                     |                |              |                |                   |             | 00000000    |

| 12H     | T2CON  |              | TOUTPS3                                                    | TOUTPS2             | TOUTPS1        | TOUTPS0      | TMR2ON         | T2CKPS1           | T2CKPS0     | -0000000    |

| 1EH     | ADRESH | High byte o  | f A/D result regis                                         | ster                |                |              | •              | •                 | •           | xxxxxxx     |

| 1FH     | ADCON0 | ADCS1        | ADCS0                                                      | CHS3                | CHS2           | CHS1         | CHS0           | GO/ DONE          | ADON        | 00000000    |

| Address | Name       | Bit7            | Bit6                 | Bit5             | Bit4            | Bit3           | Bit2             | Bit1             | Bit0       | Reset value |

|---------|------------|-----------------|----------------------|------------------|-----------------|----------------|------------------|------------------|------------|-------------|

| 80H     | INDF       | Addressing th   | is unit will use FSR | (not physical re | egister)        |                |                  |                  |            | xxxxxxx     |

| 81H     | OPTION_REG |                 | INTEDG               | T0CS             | T0SE            | PSA            | PS2              | PS1              | PS0        | -1111011    |

| 82H     | PCL        | Low byte of th  | e program counter    | (PC)             |                 |                |                  |                  |            | 00000000    |

| 83H     | STATUS     | IRP             | RP1                  | RP0              | ТО              | PD             | Z                | DC               | С          | 00011xxx    |

| 84H     | FSR        | Indirect data r | nemory address po    | ointer           |                 |                |                  |                  |            | xxxxxxx     |

| 85H     | TRISA      | TRISA7          | TRISA6               | TRISA5           | TRISA4          | TRISA3         | TRISA2           | TRISA1           | TRISA0     | 11111111    |

| 86H     | TRISB      |                 |                      | TRISB5           | TRISB4          | TRISB3         | TRISB2           | TRISB1           | TRISB0     | 111111      |

| 87H     | IOCA       | IOCA7           | IOCA6                | IOCA5            | IOCA4           | IOCA3          | IOCA2            | IOCA1            | IOCA0      | 00000000    |

| 8AH     | PCLATH     |                 |                      |                  |                 | Write buffer f | or the high 4 bi | ts of the progra | am counter | 0000        |

| 8BH     | INTCON     | GIE             | PEIE                 | T01E             | INTE            | RBIE           | TOIF             | INTF             | RBIF       | 00000000    |

| 8CH     | PIE1       | RAIE            | ADIE                 |                  |                 | EEIE           | PWMIE            | TMR2IE           | TMR1IE     | 00000000    |

| 8DH     | PIE2       |                 |                      |                  |                 |                |                  |                  | LVDIE      | 0           |

| 8FH     | OSCCON     |                 | IRCF2                | IRCF1            | IRCF0           |                |                  |                  | SCS        | -1100       |

| 90H     | OSCTUNE    |                 |                      |                  | TUN4            | TUN3           | TUN2             | TUN1             | TUN0       | 00000       |

| 92H     | PR2        | TIMER2 cycle    | register             |                  |                 |                |                  |                  |            | 11111111    |

| 93H     | PWM01DT    |                 |                      | PWM01 deadt      | time delay time |                |                  |                  |            | 00000       |

| 94H     | PWM23DT    |                 |                      | PWM23 deadt      | time delay time |                |                  |                  |            | 00000       |

| 95H     | WPUB       |                 |                      | WPUB5            | WPUB4           | WPUB3          | WPUB2            | WPUB1            | WPUB0      | 000000      |

| 96H     | IOCB       |                 |                      | IOCB5            | IOCB4           | IOCB3          | IOCB2            | IOCB1            | IOCB0      | 000000      |

| 97H     | LVDCON     | LVD_RES         | _                    | _                | _               |                | LVD_SEL[2:0]     |                  | LVDEN      | x0000       |

| 9AH     | OPA0CON    | OPA0EN          | OPA0O                | OPA0_CMP         | OPA0_ADC        | OPA0_FW        | OPA0_BG          |                  |            | 000000      |

| 9BH     | OPA0ADJ    | OPA0OUT         | OPA0COFM             | OPA0CRS          |                 |                | OPA0ADJ[4:0]     |                  |            | 000xxxxx    |

| 9CH     | OPA1CON    | OPA1EN          | OPA10                | OPA1_CMP         | OPA1_ADC        | OPA1_FW        | OPA1_BG          |                  |            | 000000      |

| 9DH     | OPA1ADJ    | OPA1OUT         | OPA1COFM             | OPA1CRS          |                 |                | OPA1ADJ[4:0]     |                  |            | 000xxxxx    |

| 9EH     | ADRESL     | Low byte of A   | DC result register   |                  |                 |                |                  |                  |            | XXXXXXXX    |

| 9FH     | ADCON1     | ADFM            |                      |                  |                 |                | LDO_EN           |                  | LDO_SEL    | 00          |

| Address | Name        | Bit7            | Bit6                  | Bit5            | Bit4         | Bit3           | Bit2            | Bit1            | Bit0        | Reset value |

|---------|-------------|-----------------|-----------------------|-----------------|--------------|----------------|-----------------|-----------------|-------------|-------------|

| 100H    | INDF        | Addressing th   | is unit will use I    | FSR (not physic | al register) |                |                 |                 |             | XXXXXXX     |

| 101H    | TMR0        | TIMER0 modu     | ule register          |                 |              |                |                 |                 |             | XXXXXXX     |

| 102H    | PCL         | Low byte of th  | e program cou         | nter (PC)       |              |                |                 |                 |             | 00000000    |

| 103H    | STATUS      | IRP             | RP1                   | RP0             | ТО           | PD             | Z               | DC              | С           | 00011xxx    |

| 104H    | FSR         | Indirect data n | nemory addres         | s pointer       |              |                |                 |                 |             | XXXXXXXX    |

| 105H    | WDTCON      |                 |                       |                 |              |                |                 |                 | SWDTEN      | 0           |

| 106H    | PORTB       |                 |                       | RB5             | RB4          | RB3            | RB2             | RB1             | RB0         | xxxxxx      |

| 107H    | PWMCON0     |                 | CLKDIV[2:0]           |                 | PWM4EN       | PWM3EN         | PWM2EN          | PWM1EN          | PWM0EN      | 00000000    |

| 108H    | PWMCON1     |                 |                       | PWM2DTEN        | PWM0DTEN     |                |                 | DT_D            | IV[1:0]     | 0000        |

| 109H    | PWMCON2     |                 |                       |                 | PWM4DIR      | PWM3DIR        | PWM2DIR         | PWM1DIR         | PWM0DIR     | 00000       |

| 10AH    | PCLATH      |                 |                       |                 |              | Write buffer f | or the high 4 b | its of the prog | ram counter | 0000        |

| 10BH    | INTCON      | GIE             | PEIE                  | TOIE            | INTE         | RBIE           | TOIF            | INTF            | RBIF        | 00000000    |

| 10CH    | EEDAT       | EEDAT7          | EEDAT6                | EEDAT5          | EEDAT4       | EEDAT3         | EEDAT2          | EEDAT1          | EEDAT0      | XXXXXXXX    |

| 10DH    | EEADR       | EEADR7          | EEADR6                | EEADR5          | EEADR4       | EEADR3         | EEADR2          | EEADR1          | EEADR0      | 00000000    |

| 10EH    | EEDATH      | EEDATH7         | EEDATH6               | EEDATH5         | EEDATH4      | EEDATH3        | EEDATH2         | EEDATH1         | EEDATH0     | XXXXXXX     |

| 10FH    | EEADRH      |                 |                       |                 |              | EEADRH3        | EEADRH2         | EEADRH1         | EEADRH0     | 0000        |

| 110H    | TABLE_SPH   |                 |                       |                 |              | Table high 4-  | bit pointer     |                 |             | XXXX        |

| 111H    | TABLE_SPL   | Table low bit p | Table low bit pointer |                 |              |                |                 |                 | XXXXXXXX    |             |

| 112H    | TABLE_DATAH | Table high bit  | pointer               |                 |              |                |                 |                 |             | XXXXXXXX    |

| 11CH    | PWMD01H     |                 |                       | PWMI            | 01[9:8]      |                |                 | PWMI            | D0[9:8]     | 0000        |

| 11DH    | PWMD23H     |                 |                       | PWMI            | 03[9:8]      |                |                 | PWMI            | D2[9:8]     | 0000        |

| Address | Name           | Bit7          | Bit6                                                      | Bit5           | Bit4        | Bit3           | Bit2            | Bit1            | Bit0        | Reset value |

|---------|----------------|---------------|-----------------------------------------------------------|----------------|-------------|----------------|-----------------|-----------------|-------------|-------------|

| 180H    | INDF           | Addressing    | Addressing this unit will use FSR (not physical register) |                |             |                |                 |                 | xxxxxxx     |             |

| 181H    | OPTION_R<br>EG | RBPU          | INTEDG                                                    | TOCS           | T0SE        | PSA            | PS2             | PS1             | PS0         | 11111011    |

| 182H    | PCL            | Low byte of   | the program co                                            | unter (PC)     |             |                |                 |                 |             | 00000000    |

| 183H    | STATUS         | IRP           | RP1                                                       | RP0            | ТО          | PD             | Z               | DC              | С           | 00011xxx    |

| 184H    | FSR            | Indirect data | a memory addre                                            | ss pointer     |             |                |                 |                 |             | XXXXXXXX    |

| 186H    | TRISB          |               |                                                           | TRISB5         | TRISB4      | TRISB73        | TRISB2          | TRISB1          | TRISB0      | 111111      |

| 188H    | ANSEL          | ANS7          | ANS6                                                      | ANS5           | ANS4        | ANS3           | ANS2            | ANS1            |             | 0000000-    |

| 189H    | ANSELH         |               |                                                           | ANS13          | ANS12       | ANS11          | ANS10           | ANS9            | ANS8        | 000000      |

| 18AH    | PCLATH         |               |                                                           |                |             | Write buffer f | or the high 4 b | its of the prog | ram counter | 0000        |

| 18BH    | INTCON         | GIE           | PEIE                                                      | T01E           | INTE        | RBIE           | T01F            | INTF            | RBIF        | 00000000    |

| 18CH    | EECON1         | EEPGD         |                                                           |                |             | WRERR          | WREN            | WR              | RD          | 0x000       |

| 18DH    | EECON2         | EEPROM c      | ontrol register 2                                         | (not a physica | l register) |                |                 |                 |             |             |

| 18EH    | WPUA           | WPUA7         | WPUA6                                                     | WPUA5          | WPUA4       | WPUA3          | WPUA2           | WPUA1           | WPUA0       | 00000000    |

| 18FH    | PWMTL          | PWM0-3 cy     | cle low bit regist                                        | er             |             |                |                 |                 |             | 00000000    |

| 190H    | PWMTH          | PWM cycle     | high bit register                                         |                |             |                |                 |                 |             | 00000000    |

| 191H    | PWMT4L         | PWM4 cycle    | e low bit register                                        |                |             |                |                 |                 |             | 00000000    |

| 193H    | PWMD0L         | PWM0 duty     | PWM0 duty ccle low bit register                           |                |             |                |                 |                 | 00000000    |             |

| 194H    | PWMD1L         | PWM1 duty     | PWM1 duty cycle low bit register                          |                |             |                |                 |                 | 00000000    |             |

| 195H    | PWMD2L         | PWM2 duty     | PWM2 duty cycle low bit register                          |                |             |                |                 |                 | 00000000    |             |

| 196H    | PWMD3L         | PWM3 duty     | cycle low bit reg                                         | gister         |             |                |                 |                 |             | 00000000    |

| 197H    | PWMD4L         | PWM4 duty     | cycle low bit reg                                         | gister         |             |                |                 |                 |             | 00000000    |

# 2.2 Addressing modes

#### 2.2.1 Direct addressing

The RAM is operated through the accumulator (ACC).

Example: pass the value in ACC to 30H register

LD 30H,A

Example: pass the value in 30H register to ACC

LD A,30H

#### 2.2.2 Immediate addressing

Pass the immediate value to accumulator (ACC).

Example: pass immediate value 12H to ACC

LDIA 12H

#### 2.2.3 Indirect addressing

Data memory can be direct or indirect addressing. Direct addressing can be achieved through INDF register, INDF is not physical register. When load/save value in INDF, address is the value in FSR register (lower 8 bits) and IRP bit in STATUS register (9th bit), and point to the register of this address. Therefore, after setting the FSR register and the IRP bit of STATUS register, INDF register can be regarded as purpose register. Read INDF (FSR=0) indirectly will produce 00H. Write INDF register indirectly will cause an empty action. The following example shows how indirect addressing works.

Example: application of FSR and INDF

| LDIA | A 30H        |                                                                     |

|------|--------------|---------------------------------------------------------------------|

| LD   | FSR,A        | ;Points to 30H for indirect addressing                              |

| CLR  | B STATUS,IRP | ;clear the 9 <sup>th</sup> bit of pointer                           |

| CLR  | INDF         | ;clear INDF, which mean clear the 30H address RAM tha FSR points to |

#### Example: clear RAM (20H-7FH) for indirect addressing:

| <u> </u> | ,    |            | 5                                      |

|----------|------|------------|----------------------------------------|

|          | LDIA | 1FH        |                                        |

|          | LD   | FSR,A      | ;Points to 1FH for indirect addressing |

|          | CLRB | STATUS,IRP |                                        |

| LOOP:    |      |            |                                        |

|          | INCR | FSR        | ;address add 1, initial address is 30H |

|          | CLR  | INDF       | ;clear the address where FSR points to |

|          | LDIA | 7FH        |                                        |

|          | SUBA | FSR        |                                        |

|          | SNZB | STATUS,C   | ;clear until the address of FSR is 7FH |

|          | JP   | LOOP       |                                        |

#### 2.3 Stack

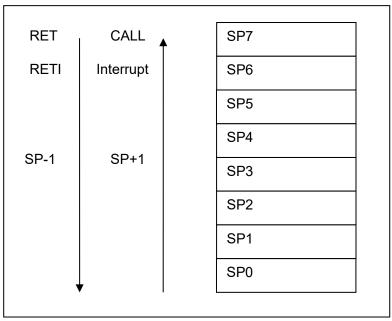

The stack buffer of the chip has 8 levels. The stack buffer is neither part of the data memory nor part of the program memory, and it can neither be read nor written. Operation on stack buffer is through stack pointers, which also cannot be written nor read. After system resets, SP points to the top of the stack. When subroutine calls or interrupts happens, value in program counter (PC)will be transferred to stack buffer. When return from interrupt or return from subroutine, value is transferred back to PC. The diagram below illustrates how this works:

Figure 2-1: How the stack buffer works

Stack buffer will follow one principle: 'first in last out'

Note: stack buffer has only 8 levels, if the stack is full and interrupt happens which cannot be screened out, then only the flag bit of the interrupt will be noted down. The response for the interrupt will be suppressed until the pointer of stack starts to decrease. This feature can prevent overflow of the stack caused by interrupt. Similarly, when stack is full and subroutine calls, then stack will overflow and the contents which enter the stack first will be lost, only the last 8 return address will be saved.

# 2.4 Accumulator (ACC)

#### 2.4.1 Overview

ALU is the 8-bit arithmetic-logic unit. All math and logic related calculations in MCU are done by ALU. It can perform addition, subtraction, shift and logical calculation on data; ALU can also control STATUS to represent the status of of the calculation results.

ACC register is an 8-bit register to store the product of calculation of ALU. It does not belong to data memory. It is in CPU and used by ALU during calculation. Hence it cannot be addressed. It can only be used through the instructions provided.

#### 2.4.2 ACC applications

#### Example: use ACC for data transfer

| •  |       |                                        |  |

|----|-------|----------------------------------------|--|

| LD | A,R01 | ;pass the value in register R01 to ACC |  |

| LD | R02,A | ;pass the value in ACC to register R02 |  |

#### Example: use ACC for immediate addressing

|       |     | <u> </u>                                                                          |

|-------|-----|-----------------------------------------------------------------------------------|

| LDIA  | 30H | ;load the ACC as 30H                                                              |

| ANDIA | 30H | ;run 'AND' between value in ACC and immediate number 30H, save the result in ACC  |

| XORIA | 30H | ; run 'XOR' between value in ACC and immediate number 30H, save the result in ACC |

#### Example: use ACC as the first operand of the double operand instructions

| HSUBA | R01 | ;ACC-R01, save the result in ACC |

|-------|-----|----------------------------------|

| HSUBR | R01 | ;ACC-R01, save the result in R01 |

#### Example: use ACC as the second operand of the double operand instructions

| SUBA | R01 | ;R01-ACC, save the result in ACC |  |

|------|-----|----------------------------------|--|

| SUBR | R01 | ;R01-ACC, save the result in R01 |  |

# 2.5 Program status register (STATUS)

STATUS register includes:

- Arithmetic status of ALU.

- Reset status.

- Selection bit of Data memory (GPR and SFR)

Just like other registers, STATUS register can be the target register of any other instruction. If an instruction that affects Z, DC or C bit that use STATUS as target register, then it cannot write on these 3 status bits. These bits are cleared or set to 1 according to device logic. TO and PD bit also cannot be written. Hence the instructions which use STATUS as target instruction may not result in what is predicted.

For example, CLRSTATUS will clear higher 3 bits and set the Z bit to 1. Hence the value of STATUS will be 000u u1uu (u = unchange). Hence, it is recommended to only use CLRB, SETB, SWAPA and SWAPR instructions to change STATUS register because these will not affect any status bits.

Program status register: STATUS (03H)

| 03H         | Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|-------------|------|------|------|------|------|------|------|------|

| STATUS      | IRP  | RP1  | RP0  | TO   | PD   | Z    | DC   | С    |

| Read/write  | R/W  |

| Reset value | 0    | 0    | 0    | 1    | 1    | Χ    | X    | X    |

Bit7 Selection bit of register memory (for indirect addressing) IRP: Bank2 and Bank3 (100h-1FFh); Bank0 and Bank1 (00h-FFh). Bit6~Bit5 RP[1:0]: Selection bit of memory; 00: Select Bank 0; 01: Select Bank 1; Select Bank 2: 10: 11: Select Bank 3. Time out bit: Bit4 TO: Power on or CLRWDT instructions or STOP instructions; WDT time out. Bit3 PD: Power down bit: Power on or CLRWDT instructions: STOP instructions. Bit2 Z: Result is zero bit: Result is 0; Result is not 0 0=Bit1 DC: Carry bit: When carry happens to higher bits or no borrow happens in Lower 4 bits in the result; When no carry happens to higher bits or borrow happens in Lower 4 bits in the result. Bit0 C: Carry/borrow bit; When carry happens at the highest bit or no borrow happens;

When no carry happens at the highest bit or borrow happens

TO and PD bit can reflect the reason for reset of chip. The following is the events which affects the TO and PD and the status of TO and PD after these resets.

| Events              | ТО | PD |

|---------------------|----|----|

| Power on            | 1  | 1  |

| WDT overflow        | 0  | X  |

| STOP instructions   | 1  | 0  |

| CLRWDT instructions | 1  | 1  |

| Sleep               | 1  | 0  |

| <b>Events</b> | which  | affect " | TO/PD |

|---------------|--------|----------|-------|

|               | WHILLI | aneci    | IU/FU |

| ТО | PD | Reset reason                  |

|----|----|-------------------------------|

| 0  | 0  | WDT overflow awaken MCU       |

| 0  | 1  | WDT overflow non-sleep status |

| 1  | 1  | Power on                      |

TO/PD status after reset

# 2.6 Pre-scaler (OPTION\_REG)

OPTION\_REG register can be read or written. Each control bit for configuration is as follow:

- ◆ TIMER0/WDT pre-scaler

- ◆ TIMER0

Pre-scaler: OPTION REG (81H)

| 81H         | Bit7 | Bit6   | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|-------------|------|--------|------|------|------|------|------|------|

| OPTION_REG  |      | INTEDG | T0CS | T0SE | PSA  | PS2  | PS1  | PS0  |

| Read/write  |      | R/W    | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| Reset value |      | 1      | 1    | 1    | 1    | 0    | 1    | 1    |

| Bit7      | Not used |                                                          |                                             |           |                                    |               |  |

|-----------|----------|----------------------------------------------------------|---------------------------------------------|-----------|------------------------------------|---------------|--|

| Bit6      | INTEDG:  | Edge                                                     | Edge selection bit for triggering interrupt |           |                                    |               |  |

|           | 1=       | INT pi                                                   | INT pin rising edge triggered interrupt     |           |                                    |               |  |

|           | 0=       | INT pi                                                   | in falling                                  | gedge tri | ggered interrupt                   |               |  |

| Bit5      | T0CS:    | Selec                                                    | tion bit f                                  | or TIME   | R0 clock source.                   |               |  |

|           | 0=       | Intern                                                   | al instru                                   | ictions p | eriod clock (F <sub>SYS</sub> /4). |               |  |

|           | 1=       | Transition edge on T0CKI pin                             |                                             |           |                                    |               |  |

| Bit4      | T0SE:    | Edge                                                     | selectio                                    | n bit for | TIMER0 clock source                |               |  |

|           | 0=       | Increase when T0CKI pin signal transite from low to high |                                             |           |                                    |               |  |

|           | 1=       | Increase when T0CKI pin signal transite from high to low |                                             |           |                                    |               |  |

| Bit3      | PSA:     | Pre-scaler allocation                                    |                                             |           |                                    |               |  |

|           | 0=       | Pre-se                                                   | caler all                                   | ocates to | TIMER0 mod                         |               |  |

|           | 1=       | Pre-se                                                   | caler all                                   | ocates to | WDT                                |               |  |

| Bit2~Bit0 | PS2~PS0: | Config                                                   | guration                                    | bit for p | re-allocation parameters.          |               |  |

|           |          | PS2                                                      | PS1                                         | PS0       | TMR0 frequency ratio               | WDT frequency |  |

| PS2 | PS1 | PS0 | TMR0 frequency ratio | WDT frequency ratio |

|-----|-----|-----|----------------------|---------------------|

| 0   | 0   | 0   | 1:2                  | 1:1                 |

| 0   | 0   | 1   | 1:4                  | 1:2                 |

| 0   | 1   | 0   | 1:8                  | 1:4                 |

| 0   | 1   | 1   | 1:16                 | 1:8                 |

| 1   | 0   | 0   | 1:32                 | 1:16                |

| 1   | 0   | 1   | 1:64                 | 1:32                |

| 1   | 1   | 0   | 1:128                | 1:64                |

| 1   | 1   | 1   | 1:256                | 1:128               |

The pre-scaler register is actually an 8-bit counter that is used as a post-scaler when used for the monitoring register WDT and as a pre-scaler when used for the timer/counter, often collectively referred to as a pre-scaler. There is only one physical divider on the chip, which can only be used for either WDT or TIMER0, and both cannot be used at the same time. That is, if it is used for TIMER0, the WDT cannot use the pre-scaler, and vice versa.

When used for WDT, the CLRWDT instruction will clear both the pre-scaler and the WDT timer.

When used for TIMER0, all instructions about writing to TIMER0 (e.g., CLRTMR0, SETB TMR0,1, etc.) will clear the pre-scaler.

Whether TIMER0 or WDT uses a pre-scaler is completely controlled by software. It can be changed dynamically. To avoid a chip reset that should not occur, the following instruction should be executed when switching from TIMER0 to WDT.

| CLRB   | INTCON,GIE     | ;Turn off the enable bit for interrupt to avoid<br>entering interrupt during the following timings |

|--------|----------------|----------------------------------------------------------------------------------------------------|

| LDIA   | B'00000111'    |                                                                                                    |

| ORR    | OPTION_REG,A   | ;set pre-scaler as its max value                                                                   |

| CLR    | TMR0           | ;clear TMR0                                                                                        |

| SETB   | OPTION_REG,PSA | ;set pre-scaler to allocate to WDT                                                                 |

| CLRWDT |                | ;clear WDT                                                                                         |

| LDIA   | B'xxxx1xxx'    | ;set a new pre-scaler                                                                              |

| LD     | OPTION_REG,A   |                                                                                                    |

| CLRWDT |                | ;clear WDT                                                                                         |

| SETB   | INTCON,GIE     | ;when an interrupt is needed, enable bit is turned on here                                         |

When switch from WDT to TIMER0 mod, the following instructions should be executed.

| CLRWDT |              | ;clear WDT            |

|--------|--------------|-----------------------|

| LDIA   | B'00xx0xxx'  | ;set a new pre-scaler |

| LD     | OPTION_REG,A |                       |

Note: To enable TIMER0 to obtain a 1:1 prescaler ratio configuration, assign WDT to the prescaler by setting the PSA bit of the option register to 1.

### 2.7 Program counter (PC)

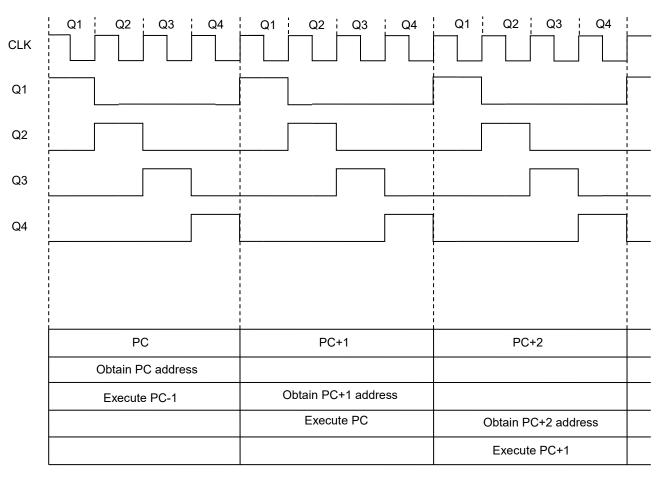

The program counter (PC) controls the order of instruction execution in the program memory FLASH, which can address the entire range of FLASH. After obtaining an instruction code, the program counter (PC) will automatically increase by 1 and point to the address of the next instruction code. However, when executing operations such as jump, condition jump, assignment to PCL, subroutine call, initialization reset, interrupt, interrupt return, subroutine return, etc., the PC will load the address associated with the instruction, rather than the address of the next instruction.

When a condition jump instruction is encountered and the jump condition is met, the next instruction read during the current instruction execution will be discarded and an empty instruction operation cycle will be inserted before the correct instruction is obtained. Or, the next instruction will be executed sequentially.